Understanding Spur Suppression vs Phase Noise Reduction in PLLs

In the design and application of Phase-Locked Loops (PLLs), spur suppression and phase noise reduction are critical considerations. PLLs are widely used in communication systems for frequency synthesis and clock generation. However, due to circuit non-idealities and variations, spurs and phase noise can degrade system performance. This blog explores the sources of spurs, their impact on system performance, and the trade-offs between spur suppression and phase noise reduction.

Sources of Spurs in PLLs

Spurs in PLLs are generated due to non-idealities in the circuit components. There are two primary sources of spurs:

Circuit Non-Idealities: Non-idealities in the phase-frequency detector (PFD) and charge pump can cause reference spurs. These spurs appear at multiples of the reference frequency.

- Reference Spurs: These are caused by imperfections in the PFD and charge pump circuitry. Mismatches, leakage currents, and other non-ideal behaviors in these components can lead to periodic disturbances that manifest as spurs at the output.

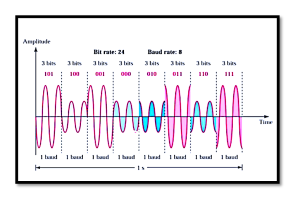

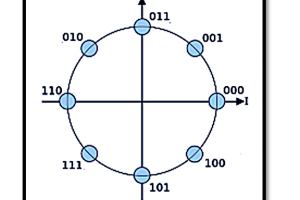

Frequency Divider Variations: Variations in the modulus of the frequency divider introduce fractional spurs. These are more challenging to mitigate because they are related to the fractional division ratio and the intrinsic operation of the divider.

- Fractional Spurs: Arising from the operation of the fractional-N divider, these spurs result from the periodic adjustment of the division ratio. The quantization noise and periodicity in the adjustment process lead to spurious tones at the output.

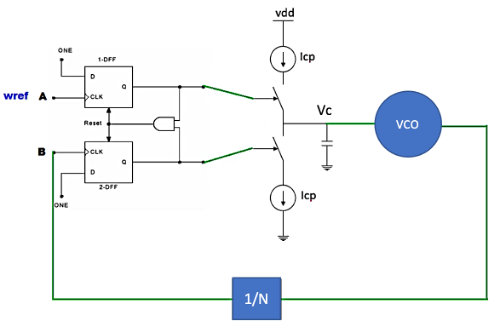

Type-II PLL Loop

A typical Type-II PLL loop includes a phase-frequency detector, a charge pump, a loop filter, a voltage-controlled oscillator (VCO), and a frequency divider. The loop works to lock the VCO output frequency to the reference frequency, scaled by the division ratio.

In this configuration:

- The PFD compares the reference frequency (Wref) with the feedback frequency from the divider.

- The charge pump produces current pulses proportional to the phase error detected by the PFD.

- The loop filter converts these pulses into a smooth control voltage (Vc) for the VCO.

- The VCO generates an output frequency that is fed back through the frequency divider to complete the loop.

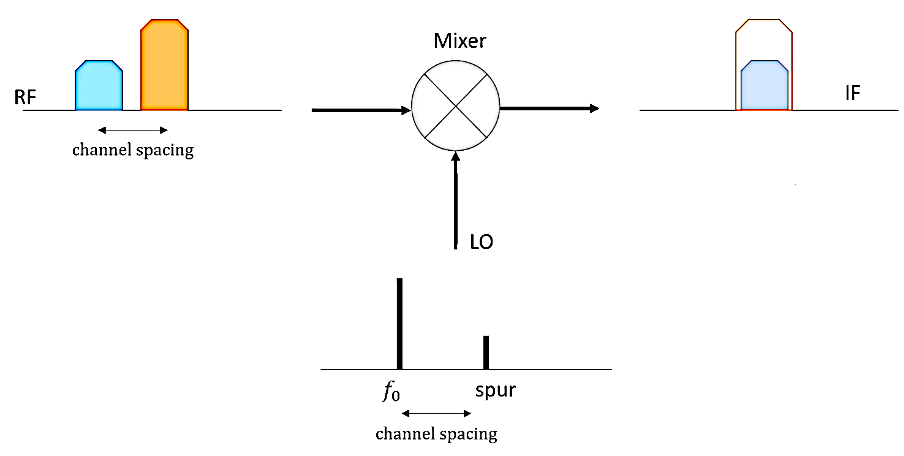

Effect of Spurs on System Performance

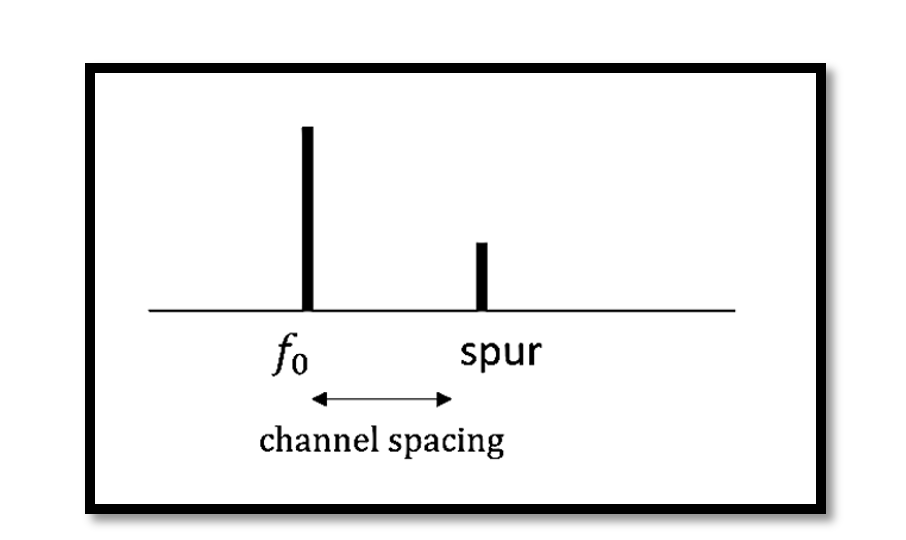

Spurs can significantly impact the performance of communication systems, particularly in mixers and frequency synthesizers. The effect of spurs includes:

- Interference with Adjacent Channels: Spurs can fall within the channel spacing and interfere with adjacent channels, leading to signal degradation.

- Mixing Products: In mixers, spurs can create unwanted mixing products, resulting in additional noise and interference at the intermediate frequency (IF).

- System Performance Degradation: Overall, spurs can reduce the signal-to-noise ratio (SNR) and degrade the performance of the communication system, leading to poor quality and reliability.

Trade-Off Between Spur Suppression and Phase Noise Reduction

There is a critical trade-off between spur suppression and phase noise reduction in PLL design. While suppressing spurs is essential for maintaining signal integrity, reducing phase noise is equally important for system performance.

- Spur Suppression: This involves techniques like improving the linearity and matching of the charge pump, optimizing the loop filter design, and using low-noise reference sources. Spur suppression focuses on minimizing the disturbances that cause spurious tones.

- Phase Noise Reduction: Reducing phase noise involves designing a VCO with low intrinsic noise, optimizing the loop bandwidth, and ensuring low-noise power supplies. Phase noise is the rapid, short-term, random fluctuations in the phase of the signal, which can affect the timing and accuracy of the PLL.

The trade-off arises because techniques to suppress spurs, such as increasing the loop bandwidth, can sometimes increase phase noise. Conversely, reducing phase noise by narrowing the loop bandwidth can make the system more susceptible to spurs.

Take our entry level course (Below) for free using coupon code RAHRF101BLOG

RF Fundamentals, Basic Concepts and Components – RAHRF101

For limited time take an additional 10% off of all our courses using coupon code RFCERT10

Rahsoft RF Certificate and courses

Conclusion

In conclusion, managing the trade-off between spur suppression and phase noise reduction is crucial in PLL design. Understanding the sources of spurs, their impact on system performance, and the interplay between different design parameters helps engineers create robust PLLs for high-performance communication systems. By carefully optimizing the design and employing advanced techniques, it is possible to achieve a balance that minimizes both spurs and phase noise, ensuring reliable and efficient operation. This blog aims to provide a comprehensive understanding of the challenges and solutions related to spur suppression and phase noise reduction in PLLs. With these insights, engineers can better tackle the complexities of PLL design and improve the overall performance of their communication systems.

Learn more about this topic by taking the complete course ‘Phase Lock Loop System Design Theory and Principles RAHRF469’. Watch the course videos for more detailed understanding. Also checkout other courses on RF system and IC design on https://rahsoft.com/courses/. Rahsoft also provides a certificate on Radio Frequency. All the courses offer step by step approach.