Understanding Type-I Phase-Locked Loops (PLLs): Design and Drawbacks

Phase-Locked Loops (PLLs) are fundamental components in modern electronic systems, widely used for synchronization purposes in communication and control systems. Among the various types of PLLs, the Type-I PLL is one of the simplest forms. This blog aims to provide an in-depth analysis of Type-I PLLs, their operational principles, and the primary challenges associated with their design.

Operational Overview of Type-I PLL

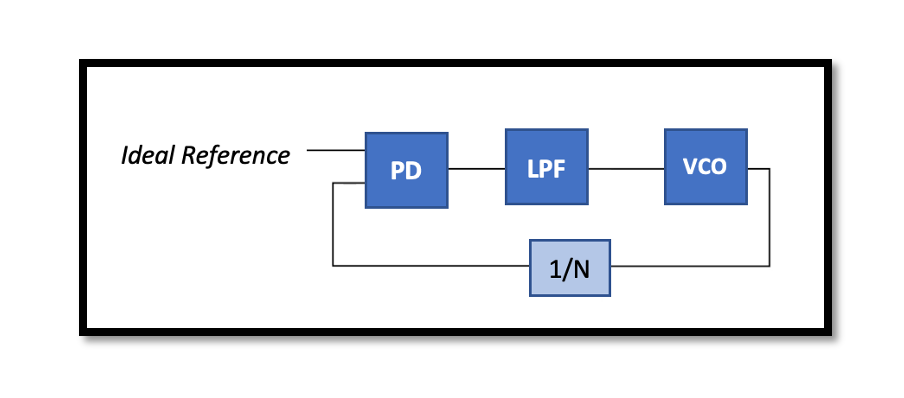

A Type-I PLL consists of the following key components:

- Phase Detector (PD): Compares the phase of the input signal with the phase of the output signal and generates an error signal proportional to the phase difference.

- Low Pass Filter (LPF): Filters the high-frequency components from the phase detector output, leaving a smooth control signal.

- Voltage-Controlled Oscillator (VCO): Adjusts its frequency based on the control signal from the LPF, thereby aligning the phase of the VCO output with the reference signal.

- Frequency Divider (1/N): Divides the VCO output frequency to provide feedback to the phase detector.

Key Parameters and Stability Considerations

In analyzing the stability and performance of a Type-I PLL, two critical parameters are considered: the VCO gain (𝐾𝑉𝐶𝑂) and the cut-off frequency of the LPF (𝑤𝐿𝑃𝐹).

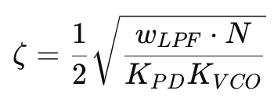

Damping Factor (𝜁):

Here, 𝐾𝑃𝐷 is the gain of the phase detector, and 𝑁 is the division factor of the frequency divider. The damping factor is a measure of system stability. A well-damped system (𝜁>1) is more stable, while an underdamped system (𝜁<1) may oscillate.

Proportionality Considerations:

- 𝜁 is inversely proportional to 𝐾𝑉𝐶𝑂. Increasing 𝐾𝑉𝐶𝑂 reduces the phase margin, leading to potential instability.

- ζ is proportional to 𝑤𝐿𝑃𝐹. However, reducing 𝑤𝐿𝑃𝐹 to decrease 𝑉𝑐𝑜𝑛𝑡ripple can cause instability.

Drawbacks of Type-I PLLs

Despite their simplicity, Type-I PLLs face several significant drawbacks:

- Stability Issues: Higher loop gain, resulting from increased 𝐾𝑉𝐶𝑂, leads to reduced phase margin and stability. Ensuring the system remains stable requires careful balancing of the loop gain.

- Ripple and Instability: Lowering the cut-off frequency of the LPF (𝑤𝐿𝑃𝐹) to reduce ripple in the control voltage can lead to instability. This trade-off between ripple suppression and stability is a central challenge in Type-I PLL design.

- Limited Acquisition Range: Type-I PLLs suffer from a limited “acquisition range.” If the VCO frequency and the input frequency are significantly different at startup, the loop may never lock, making initial synchronization challenging.

Take our entry level course (Below) for free using coupon code RAHRF101BLOG

RF Fundamentals, Basic Concepts and Components – RAHRF101

For limited time take an additional 10% off of all our courses using coupon code RFCERT10

Rahsoft RF Certificate and courses

Conclusion

Type-I PLLs offer a straightforward design but come with inherent challenges, particularly in achieving a stable lock over a wide range of frequencies. Their susceptibility to stability issues due to higher loop gain and the delicate balance required in setting the LPF parameters are crucial considerations for designers.

Understanding these nuances is essential for effective PLL design, ensuring robust performance in various applications, from telecommunications to digital circuits. By acknowledging and addressing the limitations of Type-I PLLs, engineers can better leverage their simplicity while mitigating potential issues, paving the way for more reliable and efficient systems.

Learn more about this topic by taking the complete course ‘Phase Lock Loop System Design Theory and Principles RAHRF469’. Watch the course videos for more detailed understanding. Also checkout other courses on RF system and IC design on https://rahsoft.com/courses/. Rahsoft also provides a certificate on Radio Frequency. All the courses offer step by step approach.

Tag:PLL, Type-I PLL