Course Title: Phase Locked Loops (PLL) Theory and Behavioral Modeling (RAHRF469)

Course Description: Unlock the secrets of one of the most crucial components in RF communication transceiver systems: Phase Locked Loops (PLL). From simple clock circuits to high-performance radio communication links and ultra-fast switching frequency synthesizers in vector network analyzers (VNA), PLLs play a central role in a variety of high-frequency applications. This course is your comprehensive guide to PLL theory, design, and behavioral modeling.

Course Highlights:

- PLL Types: Explore different types of PLLs, from basic to higher-order designs.

- Behavioral Modeling: Dive into behavioral modeling using Advanced Design System (ADS) software.

- Phase Noise Analysis: Understand the impact of phase noise in PLL systems and how to mitigate it.

Prerequisites: To succeed in this course, you should have a solid understanding of the following:

- Electronics and analog circuit design (intermediate level)

- Control Theory (basic level)

- Familiarity with ADS software

- Concepts such as open and closed-loop gain, feedback, transfer functions, phase margin, CMOS transistors, basic op-amps, and Laplace transforms.

Please note that this course involves more mathematical content than previous courses, including university-level mathematical calculations.

Instructor: Ata Sarrafi Advisor: Ahsan Ghoncheh

Course Curriculum:

PLL BASICS (11 Modules):

- Understand the significance of PLLs in RF communication systems.

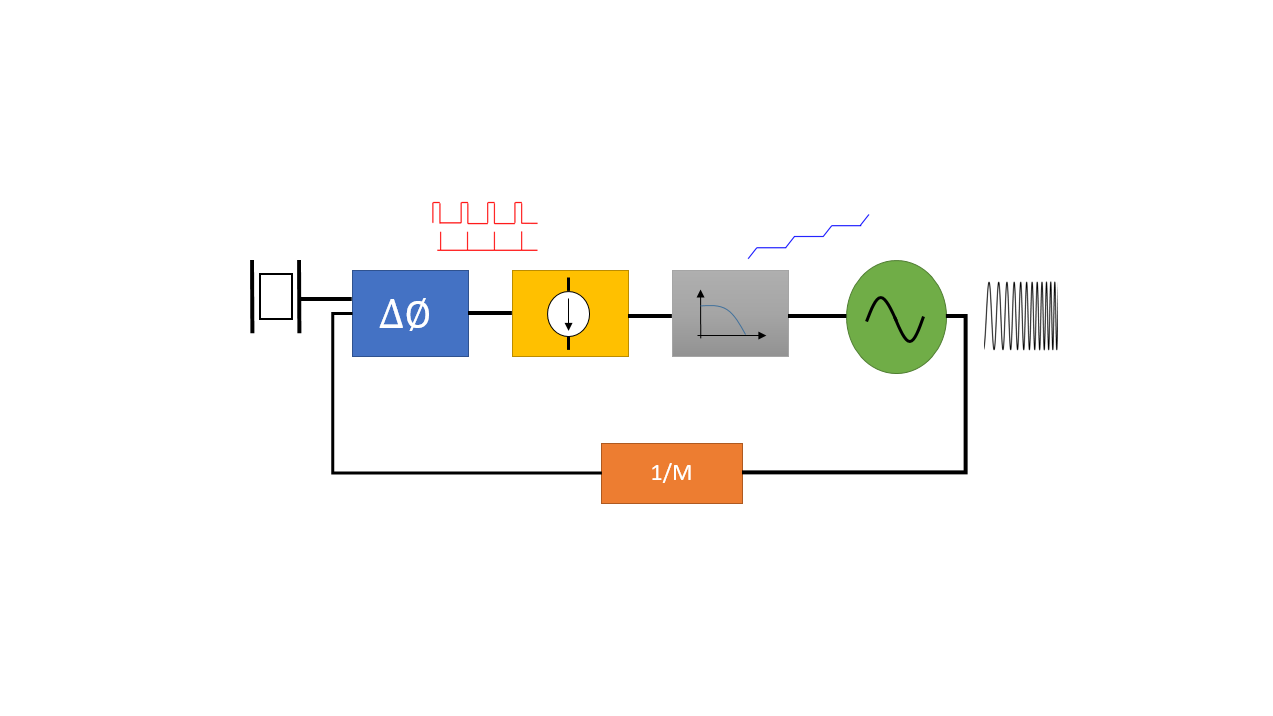

- Dive into PLL blocks, including Phase Detectors (PDs) and Voltage-Controlled Oscillators (VCOs).

- Explore PLL loop operation and transfer functions.

- Delve into the critical consideration of phase margin.

- Work through practical design examples and understand frequency multiplication.

PLL TYPES AND BEHAVIORAL SIMULATION (11 Modules):

- Learn about Type-I and Type-II PLLs.

- Explore Phase Frequency Detectors (PFDs) and Charge Pumps (CPs).

- Perform behavioral simulations of PFDs and CPs.

- Analyze the transfer function and stability of CPPLLs.

- Gain insights into open-loop bandwidth and phase margin.

- Work on numerical examples and explore higher-order PLLs.

HIGHER ORDER PLL (2 Modules):

- Discover the principles of PLL design and initial values.

- Explore 3rd order PLL filters.

ADS SIMULATION (2 Modules):

- Gain hands-on experience with ADS simulation.

- Simulate VCO divider models and PLL transient behavior.

PLL PHASE NOISE (6 Modules):

- Understand phase noise and its impact on PLLs.

- Analyze phase noise sources and their effects on VCO phase noise.

- Explore spurs and their suppression.

- Study reference phase noise and its transfer function.

- Understand the relationship between jitter and phase noise.

This course equips you with the knowledge and skills to design, simulate, and analyze PLL systems effectively. Join us in unraveling the fascinating world of Phase Locked Loops and become proficient in one of the cornerstones of RF engineering.

For a complete list of Pre-Requisite and available courses please refer to the below table:

Course Features

- Lectures 32

- Quiz 0

- Duration 6 hours

- Skill level All levels

- Language English

- Students 3310

- Certificate Yes

- Assessments Yes

Curriculum

- 5 Sections

- 32 Lessons

- 900 Weeks

- PLL BasicsPLL Basics11

- 2.1RAHRF469 Before We Start30 Minutes

- 2.2logo1 Minute

- 2.311.1.1.1 Why do we need PLL ?9 Minutes

- 2.411.1.1.2 PLL introduction15 Minutes

- 2.511.1.1.3 Ripple problem solution8 Minutes

- 2.611.1.2.1 PLL blocks – PD8 Minutes

- 2.711.1.2.2 PLL loop operation10 Minutes

- 2.811.1.2.3 PLL Transfer function14 Minutes

- 2.911.1.2.4 Phase margin consideration16 Minutes

- 2.1011.1.2.5 Design Example8 Minutes

- 2.1111.1.2.6 Frequency multiplication- practical PLL10 Minutes

- PLL Types and Behavioral Simulation11

- 3.111.1.3.1 Type-I PLL5 Minutes

- 3.211.2.1.1 Type-II PLL – PFD14 Minutes

- 3.311.2.1.2 Charge Pump10 Minutes

- 3.411.2.1.3 PFD/CP Behavioral Simulation9 Minutes

- 3.511.2.1.4 Change Pump PLL (CPLL) Transfer Function15 Minutes

- 3.611.2.1.5 Stability of simple CPPLL10 Minutes

- 3.711.2.1.6 Open loop bandwidth and Phase margin (PM)20 Minutes

- 3.811.2.1.7 Numerical Example (MATLAB)13 Minutes

- 3.911.2.1.8 Close Loop system Consideration16 Minutes

- 3.1011.2.1.9 Higher order PLL14 Minutes

- 3.1111.2.1.10 Higher order PLL in MATLAB9 Minutes

- Higher Order PLL2

- ADS simulation2

- PLL Phase noise6

- 6.111.5.1.1 PLL phase noise – Review of phase noise15 Minutes

- 6.211.5.1.2 Free running VCO phase noise ADS simulation16 Minutes

- 6.311.5.2.1 Phase noise sources in PLL and transfer function VCO phase noise17 Minutes

- 6.411.5.2.2 PLL Spurs: Spur Suppression vs Phase Noise Reduction13 Minutes

- 6.511.5.2.3 Phase Noise Sources in PLL and transfer function reference Phase Noise9 Minutes

- 6.611.5.2.4 Jitter and Phase Noise relationship9 Minutes